Advancing DDR Validation: Signal Integrity, Timing Margin, and Reliability Characterization

1. The Evolution of DDR and Why Validation Has Become Harder

2. What 'Validating DDR' Actually Means

3. Signal Integrity: When Physics Meets Design

4. Timing Verification: The Art of Counting Picoseconds

5. Simulation vs. Measurement: Bridging Design and Reality

6. Environmental Stress and Long-Term Reliability

7. Common Pitfalls and Lessons Learned

8. The Future of DDR Validation: AI, LPDDR6, and Beyond

Conclusion: From Measurement to Confidence

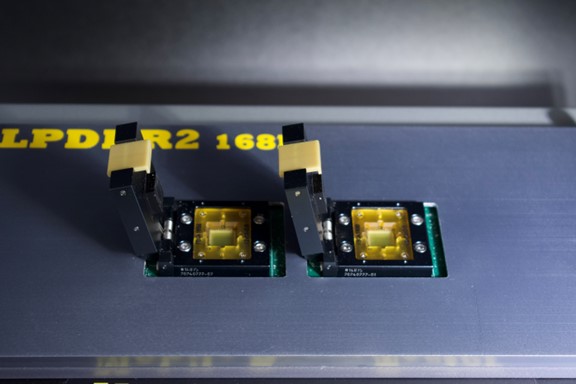

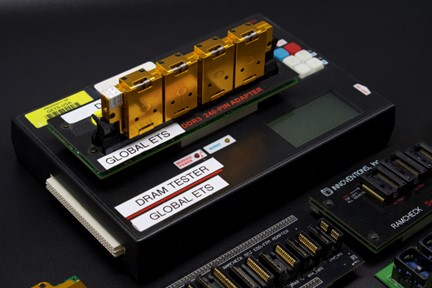

How GLOBAL ETS Engineers Ensure Memory Integrity Across Generations of DDR Technology

By GLOBAL ETS LLC — Independent Semiconductor Validation Laboratory

Introduction: The Hidden Complexity of Memory

As CPUs and AI accelerators scale beyond teraflop performance, the bandwidth and stability of DDR memory interfaces have become critical to overall system reliability. Every nanosecond of timing margin and every millivolt of signal integrity determines whether data is stored correctly or corrupted silently. From DDR3 to DDR5, data rates have grown from 1.6 Gbps to more than 6.4 Gbps per pin — an engineering leap that exposes every weakness in PCB design, firmware training, and electrical discipline.

At GLOBAL ETS LLC, we approach DDR validation as a multi-domain science. Electrical engineers, firmware specialists, and materials scientists work together to quantify stability across electrical, thermal, and temporal dimensions. Our goal is not just to prove that a memory system works, but to define how — and for how long — it will continue to work under real-world stress.

1. The Evolution of DDR and Why Validation Has Become Harder

With each generation of DDR, the operating voltage dropped, the data rate doubled, and the margins shrank. DDR4 introduced pseudo-open-drain signaling and on-die termination (ODT), while DDR5 added an integrated PMIC (Power Management IC) and doubled the burst length.

This complexity means validation now spans three layers: physical signaling (SI/PI), firmware negotiation (training algorithms), and environmental interaction (heat, noise, and vibration). Testing a DDR3 channel at 1600 MT/s might have been an oscilloscope exercise; testing DDR5 at 6400 MT/s is a multidisciplinary challenge involving high-speed instrumentation, firmware insight, and system-level correlation.

2. What 'Validating DDR' Actually Means

A DDR validation campaign is far more than confirming a successful system boot. It measures whether the memory interface maintains data integrity across all physical and environmental boundaries. GLOBAL ETS LLC divides DDR validation into four domains: signal integrity, timing margin, protocol training, and reliability characterization.

| Domain | Objective | Example Techniques |

|---|---|---|

| Signal Integrity | Quantify waveform quality, crosstalk, impedance | Oscilloscope (>20 GHz), TDR, VNA |

| Timing Margin | Measure setup/hold and skew windows | BERT sweep, eye diagram mask testing |

| Protocol & Firmware | Validate MR writes, training repeatability | Logic analyzer, DDR protocol decoder |

| Reliability & Environment | Characterize long-term drift and heat effects | Thermal chamber, voltage sweep, burn-in |

3. Signal Integrity: When Physics Meets Design

At gigahertz frequencies, every trace becomes a transmission line. Reflections, crosstalk, and impedance mismatch can turn clean square waves into distorted shapes that shrink the data eye. GLOBAL ETS engineers use time-domain reflectometry (TDR) and vector network analysis (VNA) to correlate simulation models with real waveforms.

Eye diagrams are generated by overlaying millions of transitions. A healthy DDR5 eye has a height of ~250 mV and width exceeding 0.35 UI. If that eye closes by more than 20%, bit error rates rise exponentially. We also capture jitter decomposition (random vs deterministic) to identify noise coupling between clock and strobe lines.

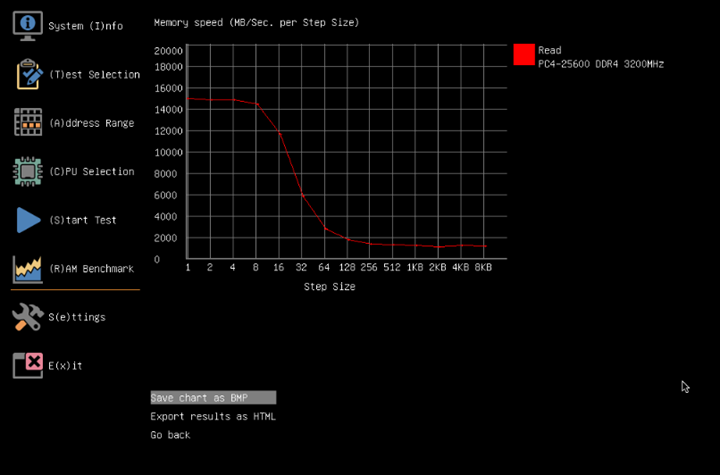

4. Timing Verification: The Art of Counting Picoseconds

At 6400 MT/s, one unit interval is only 156 ps. Ten picoseconds of timing uncertainty can break data alignment between DQS and DQ. Our automated validation scripts perform delay sweeps across temperature and voltage, logging bit-error rates to generate timing margin maps.

| Parameter | Description | Typical Range |

|---|---|---|

| tDQSS | Strobe to clock skew | ±0.25 tCK |

| tDQSQ | Data strobe to data skew | ≤0.25 UI |

| tAC | Data valid window | >150 ps |

| Jitter (RJ/DJ) | Random and deterministic jitter | <20 ps |

The collected data builds a 'timing surface' — a 3D map showing where the system remains error-free. This visualization helps OEMs tune firmware training ranges and derate frequency for reliability. In AI accelerator boards using multiple DDR5 channels, this process often reveals which lanes experience temperature-induced skew first.

5. Simulation vs. Measurement: Bridging Design and Reality

Before boards are built, SI engineers simulate DDR channels using IBIS-AMI or SPICE models. However, real PCBs differ — manufacturing tolerances, connector parasitics, and solder reflow all shift impedance. At GLOBAL ETS LLC, we overlay simulation-predicted eyes with oscilloscope captures to quantify model accuracy. When deviation exceeds 10%, we trace the discrepancy to material properties or firmware training offsets.

This correlation step closes the loop between design and validation, reducing the guesswork that often causes late-stage timing failures.

6. Environmental Stress and Long-Term Reliability

DDR validation does not end with room-temperature success. We perform voltage and temperature sweeps — from −40°C to +125°C — while continuously running memory stress tests. Eye width and bit-error-rate (BER) data are recorded at each thermal point.

GLOBAL ETS uses 1000-hour burn-in at 85°C to assess data retention and ECC correction behavior. These tests reveal the gradual drift of timing margins as solder joints age and material expansion alters trace impedance. Reliability curves (FIT vs. time) are generated to forecast product lifespan under real-world use.

7. Common Pitfalls and Lessons Learned

After hundreds of validation campaigns, certain themes repeat. The most common pitfalls include:

- Over-reliance on firmware auto-training — poor register initialization can hide marginal hardware.

- Neglecting power noise — PDN ripple often correlates directly with eye closure.

- Asymmetric routing in differential pairs — even small mismatches cause DQS drift.

- Temperature gradients between DIMMs — uneven heating shortens timing margins.

- Incomplete simulation correlation — assuming model accuracy without real data validation.

8. The Future of DDR Validation: AI, LPDDR6, and Beyond

As AI workloads drive higher memory throughput, validation must evolve. LPDDR5X and LPDDR6 introduce new challenges: adaptive refresh, per-bit calibration, and integrated on-die ECC. GLOBAL ETS LLC is expanding its methodology to include machine-learning-driven analysis of eye closure trends — detecting early signs of reliability drift before failure occurs.

We also foresee tighter coupling between validation and design: live feedback from oscilloscope traces feeding back into training algorithms, closing the loop between hardware and software in real time. In the era of chiplet architectures and 3D-stacked DRAM, this convergence will redefine what 'memory testing' means.

Conclusion: From Measurement to Confidence

Memory validation is not a checkbox — it is the foundation of system trust. Every stable gigabyte transferred across a DDR channel represents thousands of validated interactions between electrons, copper, and firmware logic. At GLOBAL ETS LLC, we view validation as a discipline that transforms uncertainty into measurable reliability. Our commitment is to make data integrity not a probability, but a guarantee.

About GLOBAL ETS LLC

GLOBAL ETS LLC is an ISO/IEC 17025-certified independent semiconductor testing and validation laboratory specializing in CPU, DDR memory, AI accelerator, and SoC reliability analysis. We combine high-speed instrumentation, simulation correlation, and thermal-mechanical modeling to ensure transparent, reproducible results. Our work empowers OEMs, design houses, and research institutions to build electronics that perform — and endure.

ISO 17025, AS6171, AS6081

ISO 17025, AS6171, AS6081 DLA Lab Suitability

DLA Lab Suitability ITAR

ITAR